•メモリの読み出し・書き出しは既に説明済み。

"☞ここを"参照して下さい。

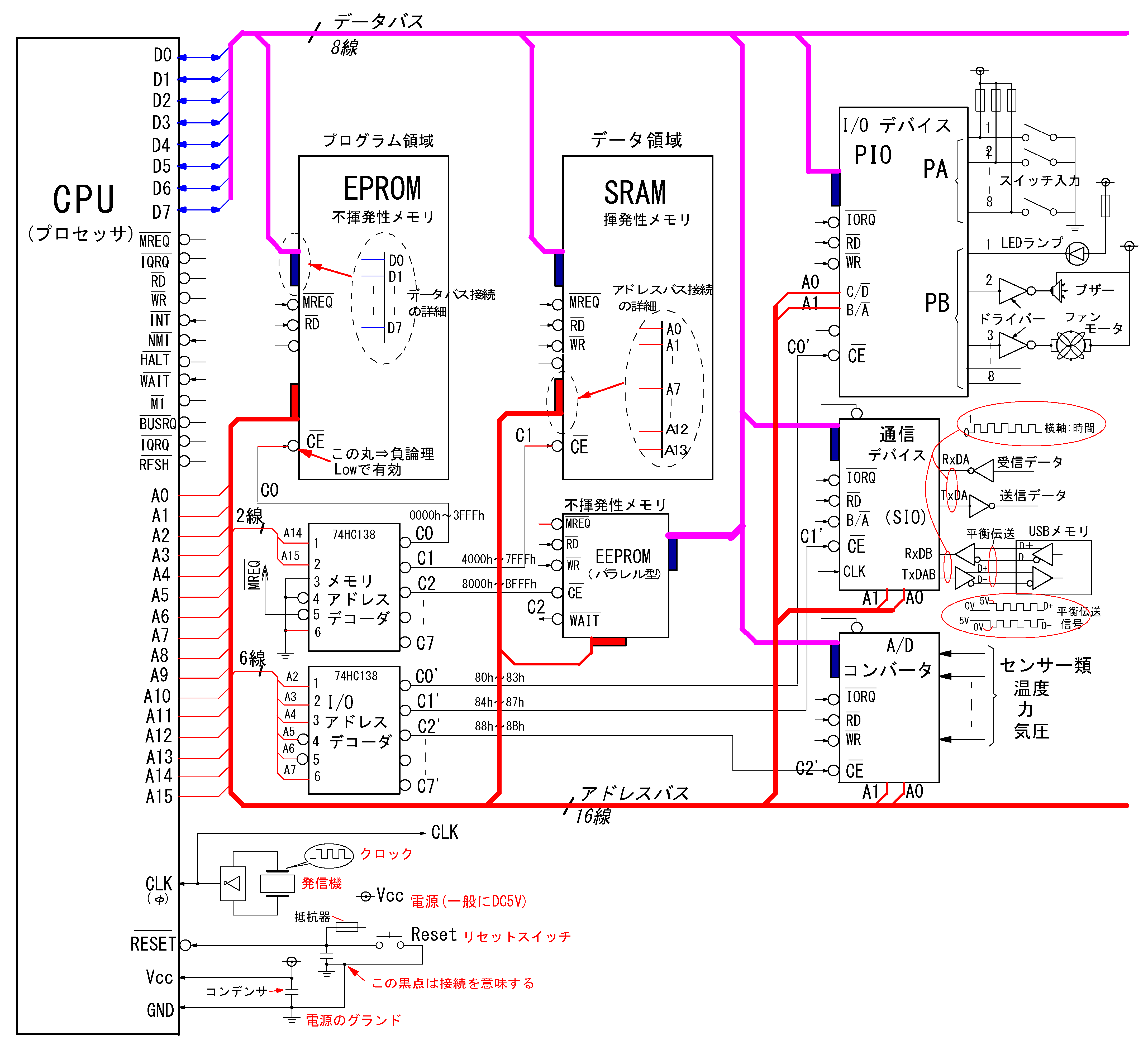

(マシンサイクルのタイムチャート)

•I/O の入力・出力のときは \(\sc{\baro{IORQ}}\)を "L" して, 次のように\(\sc{\baro{RD}}\), \(\sc{\baro{WR}}\)のいずれかを有効にする:

\(\begin{cases}

入力のとき: \sc{\baro{RD}を 'L'} \s{(を有効)} \\

出力のとき: \sc{\baro{WR}を 'L'} \s{(を有効)}

\end{cases}\)

•割り込みには最優先\(\sc{\baro{NMI}}\)と一般の\(\sc{\baro{INT}}\)があり, 異常時とか緊急時に使います。(\(\sc{\baro{NMI}}\)はリセットの次に優先度が高い)

・\(\sc{\baro{NMI}}\)

(ノンマスカラブル割り込み)はソフトでマスクできません。全てを中断して割り込み処理をする。

・\(\sc{\baro{INT}}\)

(割り込み)周辺デバイスなどの要求をうける。

割り込み処理の使用例:

・電圧を監視し, 電源断になる前に \(\sc{\baro{NMI}}\)を動作させて, 重要データを退避させてプログラムを終了させることなどのフェイルセーフをさせる。

・プログラムが正常動作の時は、定期的にウォッチドッグタイマをクリアする, クリアできなければプログラム が暴走しているとして割り込み処理/リセットさせる, またはシステムを停止(※)させる。

※停止して暴走の原因を調べられるような工夫をプログラムをしておく。

ここまでCPU を含めたマイコン全体の動きを見てきました。

次にマイコンの中心となる CPU(プロセッサ)の中の構成を見ていきましょう。

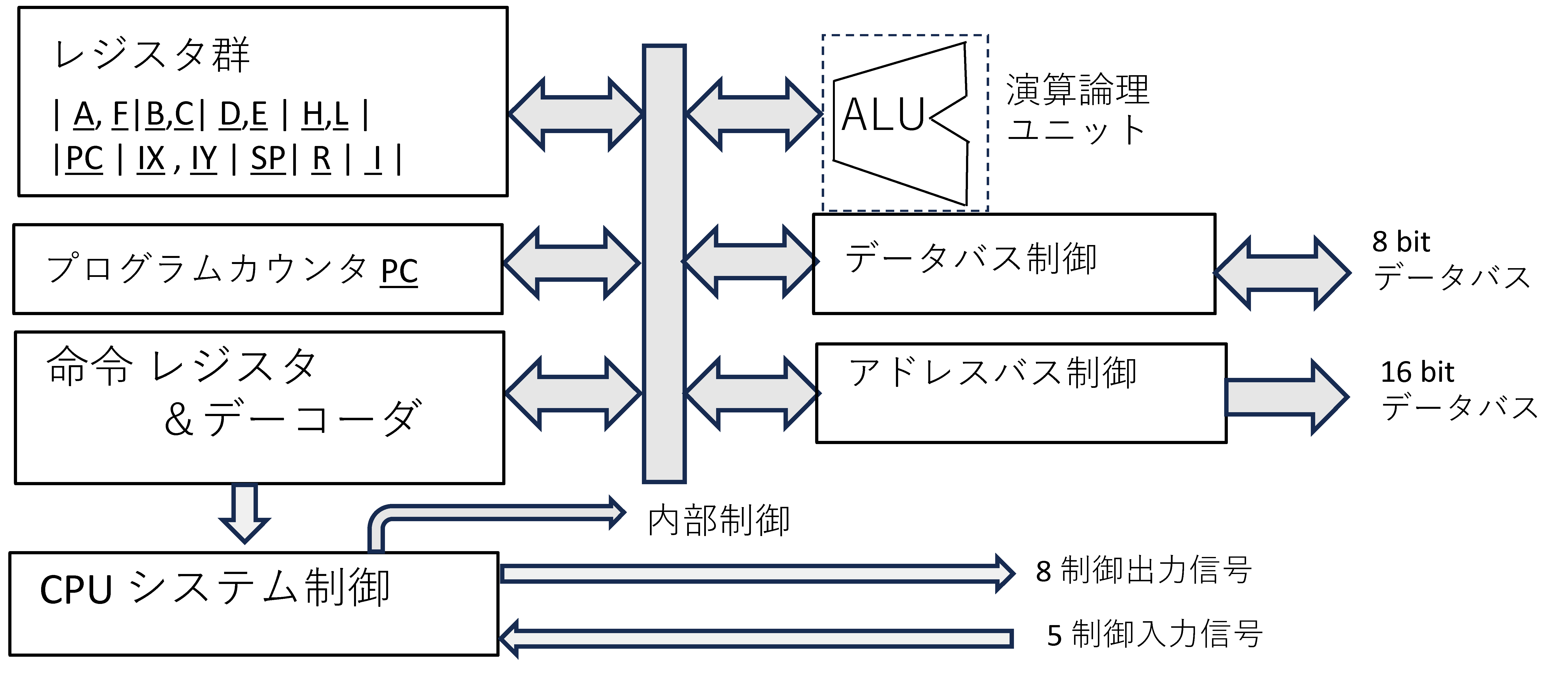

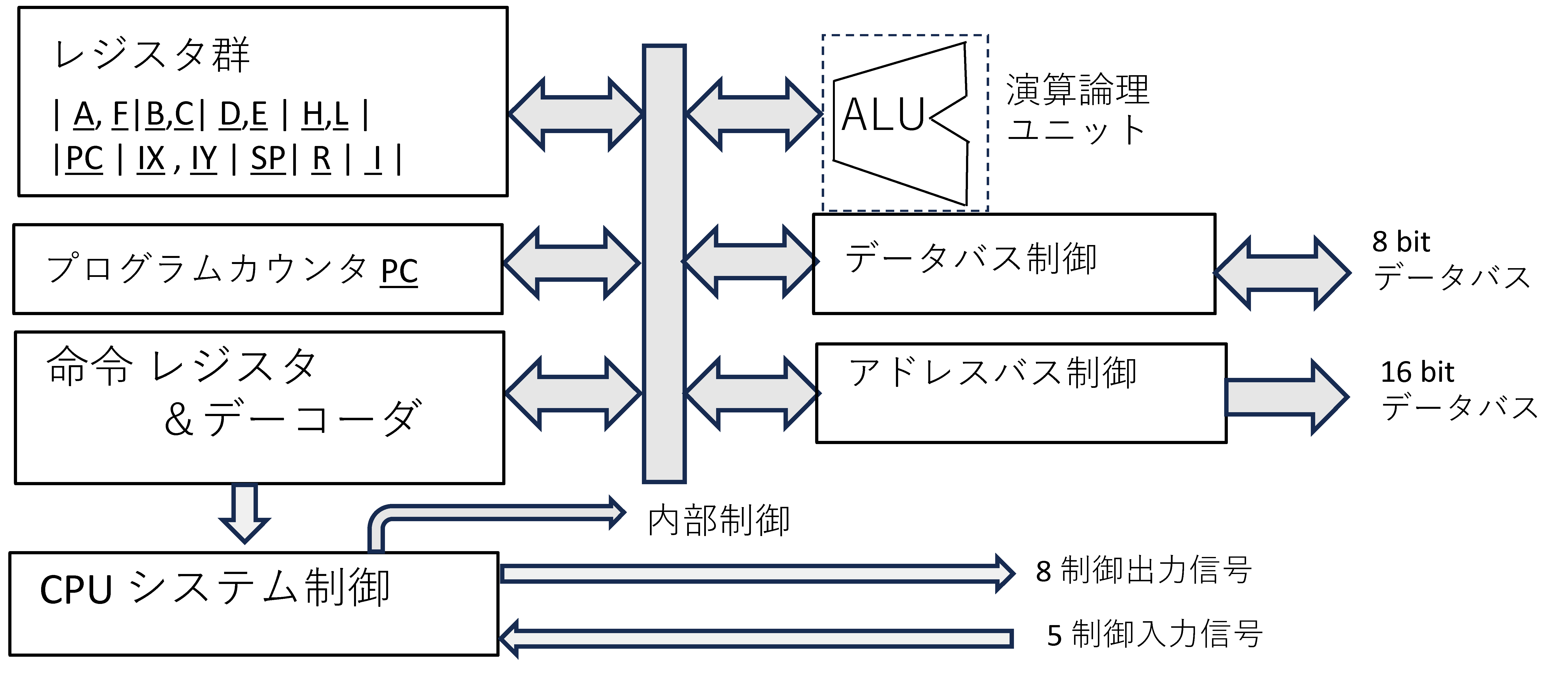

fig5 CPU 内部の構成図

1)命令デコーダを受けて制御出力信号を出します, また周辺デバイスからの制御入力信号を受けてCPUは応答します。

2)CPU は必要に応じてアドレスバス, またはデータバス に 信号を出力, またデータバスは入力/出力 を切り替えます。

3)レジスタは高速に読み書きできる CPU内部の作業用メモリです。

レジスタA:レジスタのうち " A " (アキュムレータ) は 演算の入出力データを記憶する特殊なレジスタです。(演算回路がつながっている)。

レジスタAの使用例

ADD A,(HL) : (HL)が示すメモリのデータと A の値を加算し, 結果をAに保存する。

・HLは各々8bit,2つに繋げると16bitのレジスタになる。

・例えば: HL=4FFFh, 2FFFh番地のRAMデータ=51h とし, A=21h とすると:

\(\quad \sc{\ul{A}+(HL)=21h+51h=72h \Rightarrow \ul{A}}\)

フラグF:計算結果の各種フラグを示す。例えば演算結果が負になった時, 6bit目のゼロフラグが1になる。

割り込み処理が終了すると、スタックに退避させていた情報は元に戻され、中断していたプログラムの続きが実行されます。

スタックポインタSP:割り込み要求が発生した時、直前まで実行していたプログラムのPCなどの情報を一時的に退避する場所に使わる。

IX,IY インデックス・レジスタ:このレジスタの内容に、ディスプレイメントの値を加えた値で、メモリの番地を指定できる(相対アドレス)

レジスタペア BC、DE、HL:ペア(16bit)で使うとアドレス指定に使う。 個別に使うと8bitのレジスタとして使える。

Iレジスタ:割り込みモード2の割り込みベクター(※)が入るレジスタ。

(※:割り込み処理サブルーチンの先頭番地)

Z80の割り込みはモード0, モード1,モード2があります。

モード0:Intel8080(8bit CPU)互換モード

モード1:Z80独自

モード2:Z80独自, 後の16bit CPU Intel 8086, motorola 68000にも使われた

Rレジスタ:DRAMのリフレッシュ情報。