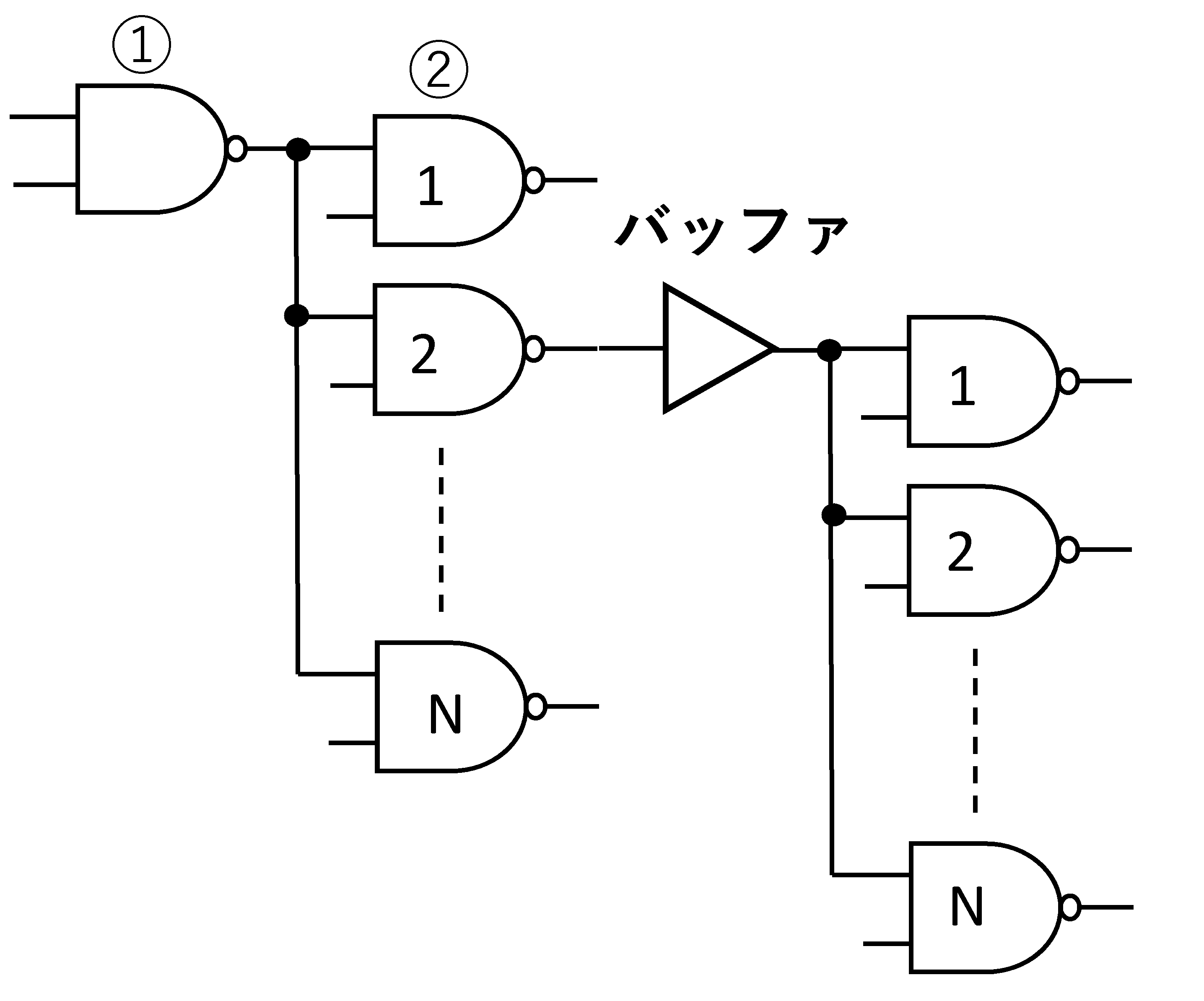

少し専門的なりますが, 異種のロジックIC(※1) を混在するときには必要な知識です。

入力信号の\(H\) と \(L\) を判定する電圧のことを

スレッショルドレベル(閾(しきい)値,threshold)と言います。

ロジックICの種類・メーカによりスレッショルドレベルが異なりますが, 以下に一例を示します。

1)

CMOS IC のスレッショルド

(電源電圧\(V_{cc}=5V\)のとき)

入力電圧 の H と L のスレッショルド

・\(H\Rightarrow V_{IH}=\ul{3.5~5V}\) ・\(L\Rightarrow V_{IL}=0~1.5V\)

出力電圧 のHとLのスレッショルド

・\(H\Rightarrow V_{OH}=\ul{4.95~5V}\) ・\(L\Rightarrow V_{IL}=0~0.05V\)

Hレベルについて :

出力は最低でも4.95Vを出力し,入力は3.5V以上を H と判別する。

\(\ul{4.95-3.5=1.45V}\)の余裕がある。

これをノイズマージンとういい, Hレベルの出力信号を3.5V(4.95-1.45)まで下がっても動作します。

L レベルについても同様の考え方です。

2)

TTL IC のスレッショルド

(電源電圧\(V_{cc}=5V\)のとき)

入力電圧のHとLのスレッショルド

・\(H\Rightarrow V_{IH}=\ul{2.0~5V}\) ・\(L\Rightarrow V_{IL}=0~0.8V\)

出力電圧のHとLのスレッショルド

・\(H\Rightarrow V_{OH}=\ul{2.4~5V}\) ・\(L\Rightarrow V_{IL}=0~0.4V\)

Hレベルについて :

上記と同様に計算して, Hレベルのノイズマージンは:\(\ul{2.4-2.0=\cl{0.4V}}\) です。

…低いですね, 出力の2.4V が何らかの原因で 0.5V低下し, 1.9V になると誤動作します。

TTLとCMOSはスレッショルド・レベルが異なるので,TTLとCMOS の混在した回路は避けるべきである。

現在, 新規設計ではTTL を使うことはないが, 混在がやむを得ずの場合,TTLでCMOSを駆動するときは配慮が必要である。